加速虛擬原型樣機開發,RTL驗證和SoC軟件驗證

基于FPGA的原型系統在運行速度和準確度上都接近流片回來的芯片,所以對于芯片完整的功能性確認以及早期軟件開發來說均具有重要意義。但是需要具備豐富的專業知識、大量資源來構建額外的硬件環境、以及互聯技術方案,才能構建一個符合標準的原型驗證系統。

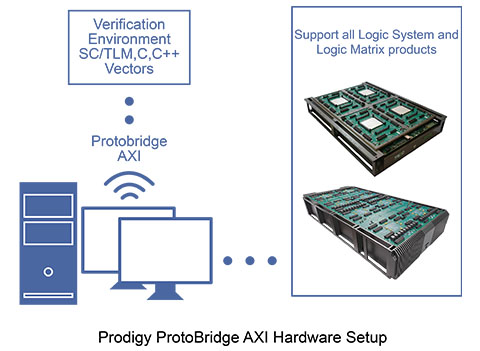

芯神瞳協同仿真軟件ProtoBridge通過采用業內廣泛使用的 AXI-4 總線協議以及獨有的專利技術*,實現了將設計鏈接到 FPGA 原型驗證環境。它建立了一個高吞吐量的數據通道,允許大量的事務級數據在 FPGA 與 PC 主機之間進行交互。

產品特征

用來進行 FPGA 集成的 AXI-4 事務級互連模塊主從接口

在計算機上的一組用來執行 AXI 總線功能的 C-API 函數

針對 Linux 或者 Windows 系統的 PCIe Gen3 驅動程序

包含 FPGA 內部存儲演示的參考設計

系統集成指南和詳細的產品規格

* 專利號:ZL201911239764.5

在沒有完整的 SoC 設計的條件下進行早期的 IP 驗證

IP 模塊連接到 AXI 總線,可在沒有處理器內核和外設的條件下驗證

利用 FPGA 原型驗證環境在速度性能上的優勢,進行早期的算法或架構探究

通過高吞吐量的數據通道縮短驗證周期

利用事務級的驗證以確保系統結果的準確性

運用 C 代碼編寫測試激勵以減少創建 RTL 測試激勵所需的時間和精力

利用測試覆蓋率的提升,優化產品的可靠性

利用軟件創建邊緣測試案例并在 FPGA 原型上測試

使用存儲在主機上的測試向量對 FPGA 原型進行高性能回歸測試

無需額外的構建特定硬件和軟件,進而消除對資源及專門知識的限制

芯神瞳協同仿真軟件 ProtoBridge 適用于任何設計,因而可重復使用于多個項目

獲得世界領先的支持,準確及時地幫設計團隊解決問題,讓客戶專注于自己的設計本身

FPGA 端口上實例化了 AXI-4, AXI4-Lite, AXI-3 和 AHB 總線連接

可配置的數據位寬,從 32 位到 1024 位

每個主/從實例支持獨立的時鐘

8 通道的 PCIe Gen3 作為 PC 主機和 FPGA 之間的數據傳輸通道

大量的數據在 PC 主機和 FPGA 之間傳輸的速率高達 4000MB/s

支持直接訪問和 DMA 訪問模式

系統初始化函數調用以實現驗證工具環境的管理

中斷控制函數調用來標識中斷信號源,進而觸發 C-API 的后續動作

數據讀/寫函數調用,與 FPGA 電路進行數據交互

DMA 傳輸函數調用來執行大量數據的 DMA 操作

利用 PC 內存來存儲數據,以減輕待測試設計對存儲容量的需求

允許 DUT 與 PC 主機的內存進行數據交互

減少了 DUT 搬移中間數據的次數,進而簡化了后續的設計和調試流程

在 PC 同時進行其他任務的情況下,提供了方便的內存訪問功能

通過標準的基于 AXI 的 C-API 功能函數與其他的商業或者私有的驗證工具兼容

KU115/VU440 Logic Module

VUS/VU19P/VU9P/S10S/S10M Logic System

64 位 Windows 7 系統

64 位 Linux RHEL 6 系統

64 位 Ubuntu 14.04.2 系統

x8 PCIe Gen3