PegaSim芯神馳是思爾芯傾力打造的一款高性能、多語言混合的商用數字邏輯仿真器。PegaSim采用了創新的架構算法,實現了高性能的仿真引擎和約束求解器引擎,支持多種設計與驗證語言,包括SystemVerilog、Verilog、VHDL和UVM驗證方法學等。

支持IEEE1800-2017SystemVerilog,IEEE1364Verilog和IEEE1076-1993VHDL

支持UVM,VMM和OVM方法學

支持時序反標(SDF&Timing check)

完整的混合仿真DPI與VPI支持

支持自動增量和并行設計編譯技術

可媲美業內領先商用仿真器的編譯效率與運行性能

芯片驗證過程中,可以通過分析RTL 代碼的覆蓋率來衡量驗證的完備性。PegaSim集成了覆蓋率分析工具,以支持覆蓋率驅動的驗證方法,幫助定義、度量和報告代碼覆蓋率目標,并發現覆蓋率漏洞。

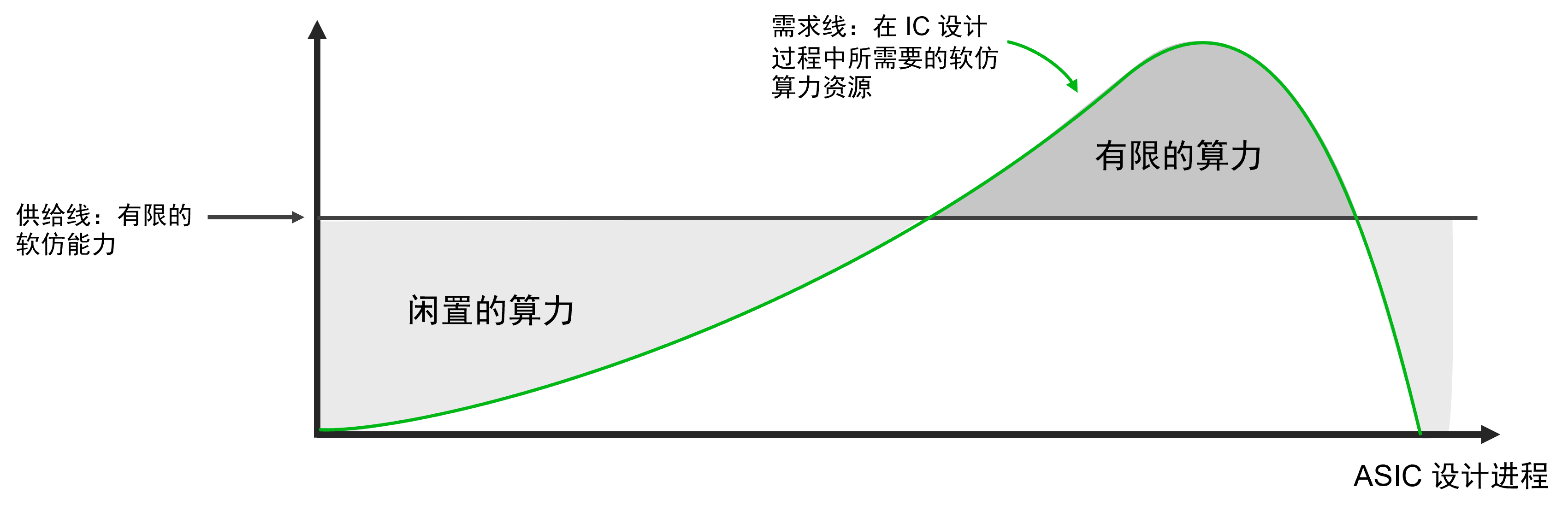

在一個芯片的開發流程中,設計工程師會應用硬件描述語言(HDL)來設計數字電路。為了保證芯片功能的正確性,在數字電路的仿真中,軟件仿真會通過計算機給出的各種測試激勵來模擬芯片在真實環境下的運行狀況。在搭建的測試環境中,軟件仿真會編譯這些代碼,并計算出仿真結果。驗證是一個不斷迭代的過程,需要不斷編寫或修改測試來覆蓋功能點和RTL代碼。在仿真過程中,不斷發現問題,更正問題,回歸測試……循環往復的同時,不斷進行功能覆蓋率、代碼覆蓋率分析,使覆蓋率趨于收斂。這種基于軟件的邏輯仿真在整個功能驗證中都需要用到。雖然軟件仿真技術對工程師來說非常有必要,但就現有的商業模式來說,軟件仿真的仿真能力和算力都與軟件許可證(software license)掛鉤。供應商提供的商用軟件仿真服務會以license的形式收費。但在實際使用時,工程師們難以依賴經驗進行有效算力與工具需求計算的匹配。

因為項目開發中對于算力的需求是波動的。有時候已購買的license無法滿足現實使用需求,有部分設計工程師獲取不到就會造成搶占或擁堵。但如果超前部署,又會帶來巨額的成本投入,有可能在閑置時造成資源的浪費。這就對芯片開發效率產生致命影響。對于企業來說怎么平衡生產和效益匹配的問題是當下急需解決的事情。

完全的并行計算

大規模彈性存儲

隨時隨地都可用

安全性能有保障

無需IT維護成本

快速可靠地完成