產(chǎn)品服務(wù)

Reduced Instruction Set Computer-Five (RISC-V)

一、RISC-V:開源與自由度的完美結(jié)合

RISC-V是一種基于“精簡指令集(RISC)”設(shè)計(jì)的開源指令集架構(gòu)。相較于ARM和x86,RISC-V的架構(gòu)更為精煉。具體而言,RISC-V的規(guī)范文檔只有145頁,而其“特權(quán)架構(gòu)文檔”更是只有91頁,這無疑為硬件和軟件開發(fā)帶來更高的效率。當(dāng)前RISC-V具有三大優(yōu)勢(shì):

模塊化設(shè)計(jì):RISC-V采用模塊化的組織結(jié)構(gòu),通過一套統(tǒng)一的指令集架構(gòu)來滿足各種不同的應(yīng)用場(chǎng)景。這種模塊化設(shè)計(jì)是x86和ARM架構(gòu)所不具備的

指令數(shù)目少:RISC-V的指令集極為精煉,基礎(chǔ)的RISC-V指令數(shù)目僅有40多條。即使加上各種模塊化擴(kuò)展,總指令數(shù)也相當(dāng)有限,這樣不僅提高了CPU的執(zhí)行效率,還降低了功耗

開源與自由度:作為一個(gè)開源架構(gòu),RISC-V有全套開源免費(fèi)的編譯器、開發(fā)工具和軟件開發(fā)環(huán)境(IDE)。這大大降低了門檻,使得任何人都可以對(duì)其進(jìn)行定制和擴(kuò)展

RISC-V以其開源和高度可定制的特性,正逐漸改變?nèi)虬雽?dǎo)體市場(chǎng)的格局,給芯片設(shè)計(jì)和制造帶來了前所未有的可能性。在全球政治經(jīng)環(huán)境日趨復(fù)雜的今天,RISC-V為我國在半導(dǎo)體領(lǐng)域的自主可控和快速發(fā)展提供了一個(gè)難得的機(jī)會(huì)

RISC-V架構(gòu)在物聯(lián)網(wǎng)(IoT)、服務(wù)器和存儲(chǔ)市場(chǎng)等多個(gè)領(lǐng)域擁有巨大的應(yīng)用潛力。在物聯(lián)網(wǎng)方面,其開源和高度可定制的特質(zhì)賦予了它快速適應(yīng)多元化市場(chǎng)需求的能力,對(duì)于個(gè)別物聯(lián)網(wǎng)的應(yīng)用都可以做個(gè)別的定制。雖然在服務(wù)器和高性能計(jì)算領(lǐng)域仍然處于初級(jí)階段,RISC-V憑借其高成本效益和靈活可定制的特點(diǎn),有很大機(jī)會(huì)突破這一市場(chǎng)。在數(shù)據(jù)存儲(chǔ)方面,隨著計(jì)算需求的增長,RISC-V的低功耗和高度定制性也呈現(xiàn)為有效的解決方案。盡管RISC-V在硬件方面具有多重優(yōu)勢(shì),但要在非IoT等復(fù)雜的市場(chǎng)環(huán)境中取得更大的成功,還需加強(qiáng)其軟件生態(tài)系統(tǒng)。與基于x86架構(gòu)的Windows或基于ARM架構(gòu)的Android相比,RISC-V目前還缺乏一個(gè)廣泛認(rèn)可的軟件棧(software stack),這在高度碎片化的IoT領(lǐng)域尤為突出。主要挑戰(zhàn)有:

碎片化與穩(wěn)定性

兼容性問題:低成本的授權(quán)方式和廠商可以自定義指令的特點(diǎn)可能會(huì)影響到RISC-V標(biāo)準(zhǔn)的持續(xù)穩(wěn)定性,以及軟件和編譯器生態(tài)系統(tǒng)的向后/向前兼容性

標(biāo)準(zhǔn)細(xì)節(jié)的挑戰(zhàn)

漫長的演變過程:在服務(wù)器和移動(dòng)設(shè)備方面,標(biāo)準(zhǔn)的細(xì)節(jié)定義存在很多需要解決的問題,這需要一個(gè)長期的演變和改進(jìn)過程

EDA支持

成熟度問題:RISC-V的應(yīng)用實(shí)例仍在不斷成熟,對(duì)于稍大型的商用設(shè)計(jì),通常需要大量修改RTL(寄存器傳輸級(jí))代碼

IP開發(fā)和適配:為了滿足多樣化的應(yīng)用需求,還需要開發(fā)新的IP(知識(shí)產(chǎn)權(quán))組件,并進(jìn)行舊有經(jīng)典IP的適配

RISC-V面臨的不僅是硬件的挑戰(zhàn),更包括軟件生態(tài)、標(biāo)準(zhǔn)化和成熟度等多方面的問題,這些都需要行業(yè)與社區(qū)的共同努力來解決

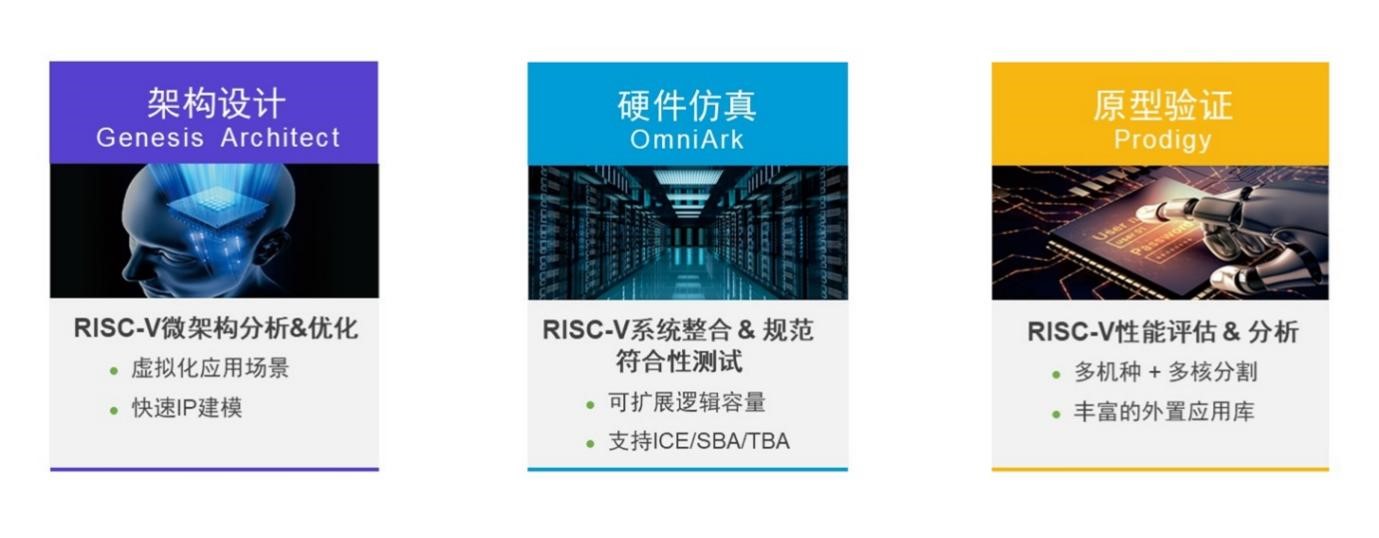

面臨這一系列多層次的問題,思爾芯一系列數(shù)字前端設(shè)計(jì)解決方案可以打造一個(gè)更高效、穩(wěn)定的RISC-V平臺(tái)。針對(duì)RISC-V,思爾芯的 “芯神匠”可提供微架構(gòu)分析和優(yōu)化,“芯神鼎”可提供系統(tǒng)的全面整合與驗(yàn)證,而“芯神瞳”可提供軟件性能評(píng)估與分析

“芯神匠”RISC-V微架構(gòu)建模:

芯神匠提供了一個(gè)建模、分析、仿真和軟硬件協(xié)作的平臺(tái),利用建模方法學(xué)實(shí)現(xiàn)電子系統(tǒng)級(jí)(Electronic System Level,ESL)設(shè)計(jì)流程,可用于開發(fā)半導(dǎo)體、航空和汽車電子系統(tǒng)設(shè)計(jì)產(chǎn)品。通過芯神匠可以進(jìn)行RSIC-V微架構(gòu)建模。芯神匠能模擬現(xiàn)有市場(chǎng)上處理器內(nèi)核的微架構(gòu)行為,并允許用戶在微架構(gòu)級(jí)別添加自定義邏輯。用戶可以輕易地調(diào)整參數(shù)以測(cè)試不同配置。例如:芯神匠支持混合處理器(Hybrid Processor)作為IP模塊進(jìn)行模擬,以反映市場(chǎng)上處理器內(nèi)核的多樣性

“芯神鼎”RISC-V系統(tǒng)的全面整合與驗(yàn)證:

芯神鼎是思爾芯自主研發(fā)的企業(yè)級(jí)硬件仿真系統(tǒng),具備超大規(guī)模可擴(kuò)展陣列架構(gòu),設(shè)計(jì)容量高達(dá)20億門。該系統(tǒng)支持多種仿真驗(yàn)證模式,如TBA和ICE,同時(shí)提供信號(hào)全可視功能。它特別針對(duì)RISC-V系統(tǒng)的全面整合與驗(yàn)證展現(xiàn)出強(qiáng)大的能力。我們正在與第三方合作深入討論,以制定相應(yīng)的規(guī)范性測(cè)試來避免系統(tǒng)碎片化的問題,并提供更多解決方案,例如系統(tǒng)一致性(System coherency)、多核并行處理(Multicore execution)、深度SoC性能分析(SoC profiling)等

“芯神瞳”RISC-V性能分析:

原型驗(yàn)證不僅滿足了硬件驗(yàn)證需求,還為芯片開發(fā)者構(gòu)建了在真實(shí)硬件上測(cè)試軟件功能與性能的平臺(tái)。軟件工程師可在此環(huán)境下直接開發(fā)和調(diào)試,顯著加速協(xié)同開發(fā)進(jìn)程。考慮到RISC-V的多種選擇,芯片開發(fā)者需對(duì)不同供應(yīng)商和配置的RISC-V核心進(jìn)行評(píng)估,從而選擇最適合的方案。思爾芯的原型驗(yàn)證系統(tǒng)能夠協(xié)助進(jìn)行SPEC跑分、IO驗(yàn)證以及bsp驅(qū)動(dòng)開發(fā)等工作,覆蓋了從硬件設(shè)計(jì)到軟件集成的全生命周期。以北京開源芯片研究院(開芯院)旗下的RISC-V處理器“香山”為例。基于思爾芯的芯神瞳VU19P原型驗(yàn)證系統(tǒng),香山團(tuán)隊(duì)運(yùn)行了SPEC基準(zhǔn)測(cè)試,通過結(jié)合顯卡運(yùn)行Linux和圖形界面,以直觀地評(píng)估其性能。這為團(tuán)隊(duì)提供了寶貴的反饋,可以據(jù)此進(jìn)行優(yōu)化以達(dá)到或超過預(yù)期的性能標(biāo)準(zhǔn)。目前,第二代“香山”(南湖架構(gòu))的SPEC2006得分為20分,性能超越了2018年的ARM Cortex-A76

RISC-V技術(shù)已深入到各個(gè)領(lǐng)域,其開源、簡潔以及高度可擴(kuò)展的特性正在重新定義計(jì)算的未來。核心指令集的開源特性為芯片設(shè)計(jì)公司提供了保證供應(yīng)鏈自主可控的可能性。同時(shí),這種共建共享的機(jī)制也促進(jìn)了RISC-V架構(gòu)的快速更新和迭代。其多樣性既是機(jī)會(huì)也是挑戰(zhàn)。思爾芯針對(duì)RISC-V微架構(gòu)分析,系統(tǒng)整合與規(guī)范符合性測(cè)試,以及提供軟件性能評(píng)估提供了多種優(yōu)化方案。期望能幫助各方更好地整合資源,擴(kuò)大RISC-V社區(qū),共推新生態(tài)發(fā)展