Advanced RISC Machines (ARM)

Arm架構在當今科技領域中占據著至關重要的地位。Arm架構憑借出色的能源效率、靈活性和性能,已經穩居全平臺主流架構之一,不僅在移動設備領域占據絕對地位,還在桌面計算、服務器領域以及云計算等高性能應用中發揮著

關鍵作用。Arm的生態系統豐富,與全球眾多合作伙伴共同推動其發展,使其在科技行業中具有廣泛的影響力。隨著技術的不斷進步和應用需求的不斷增長,Arm架構將繼續發揮其優勢。

思爾芯的Arm相關解決方案

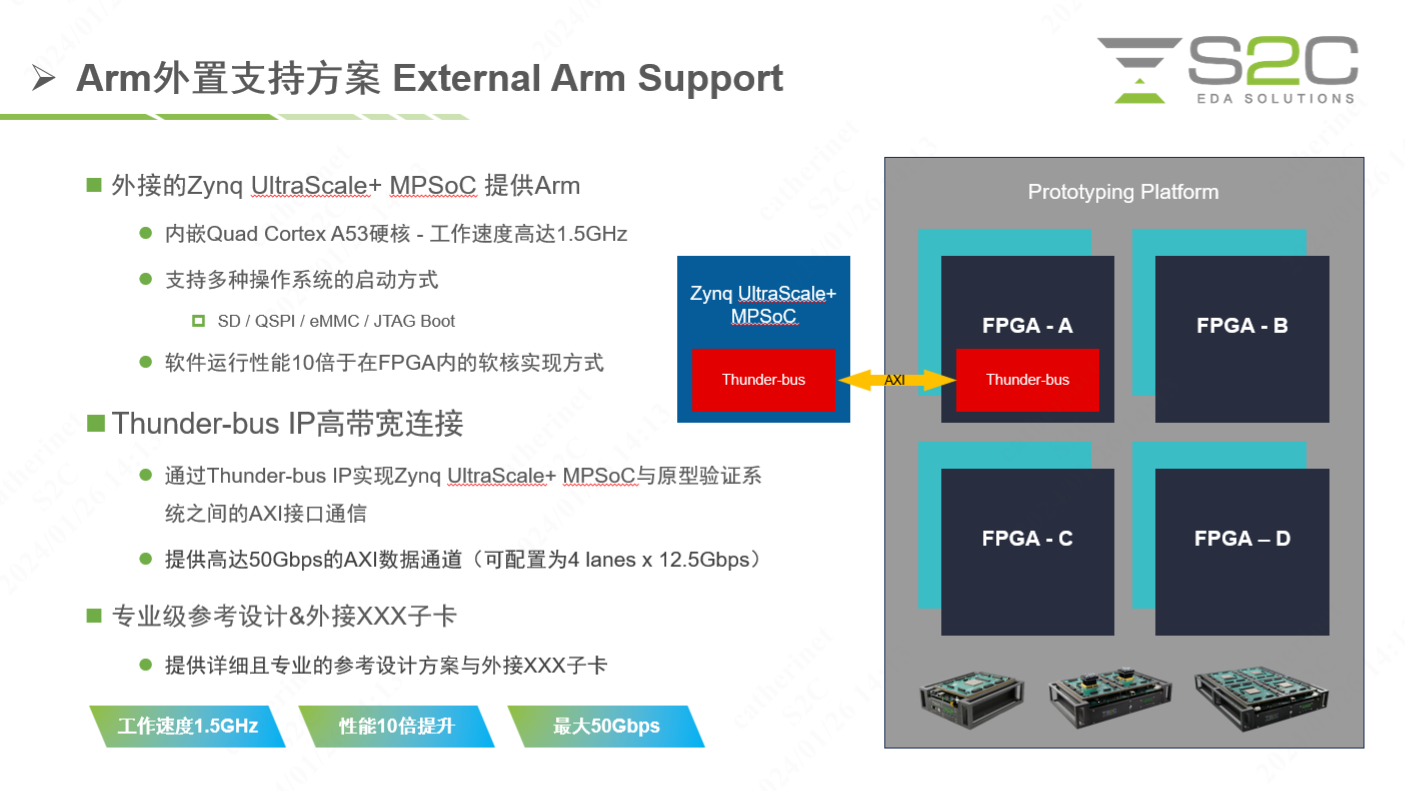

Arm外設IP的驗證或是操作通常會搭配Arm CPU核的運行。通常用戶會選擇在Zynq UltraScale+ MPSoC內驗證,因其FPGA集成了Arm 內核和 AXI 結構接口,是低門數容量驗證的最佳選擇。但是,對于規模較大的IP,受Zynq

UltraScale+ MPSoC可編程門數的限制,往往需要橋接一個更大容量的 FPGA。通過AMD-Xilinx Chip-to-Chip IP建立的片間連接,可以實現Zynq UltraScale+ MPSoC與原型驗證系統之間的AXI接口通信,數據傳輸速率高達

50Gbps。思爾芯針對Zynq UltraScale+ MPSoC開發中常用的評估板——Xilinx ZC7(ZC702/ZC706/ZCU102)提供Prodigy Zynq接口模塊,方便ZC7與芯神瞳原型驗證系統或邏輯模塊進行物理連接。

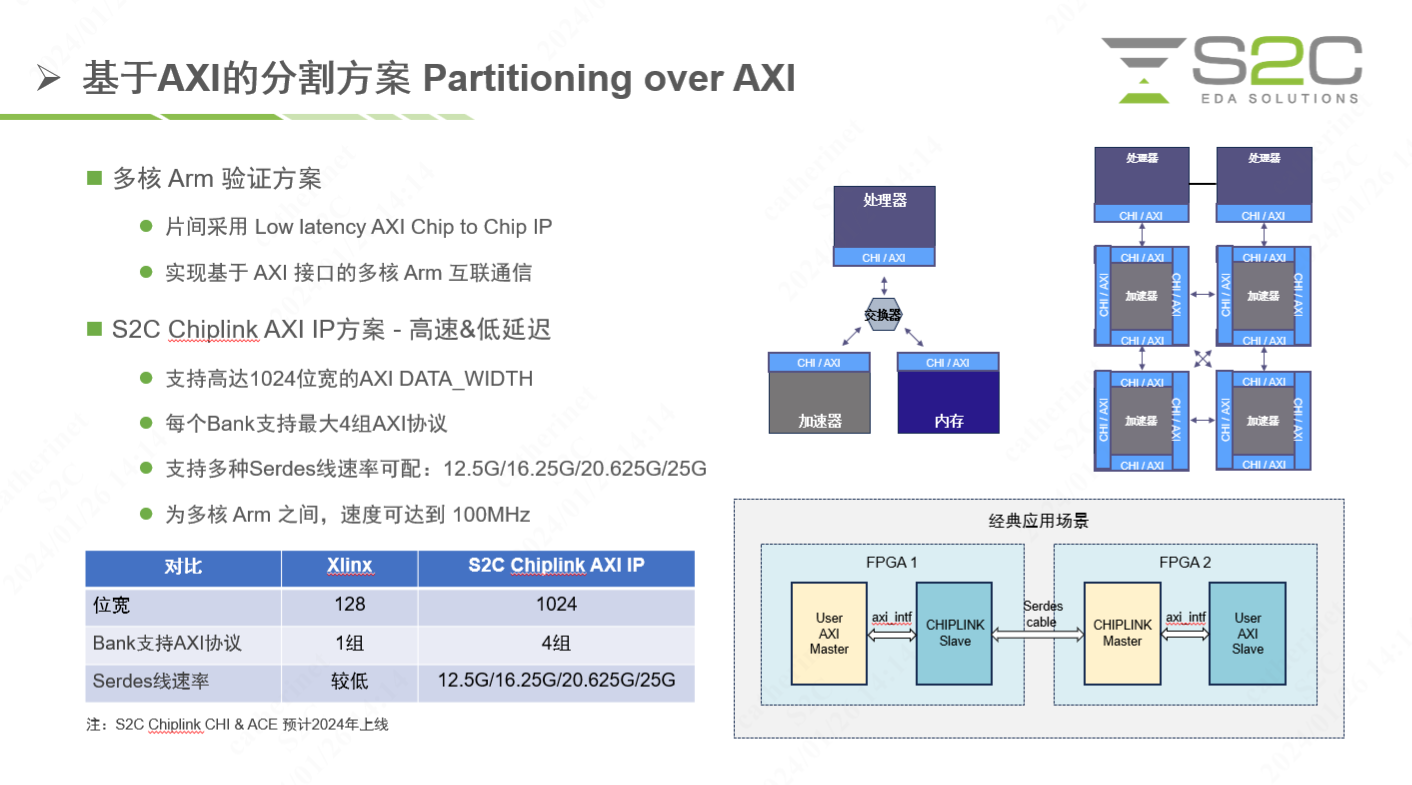

除了IP驗證,在基于Arm的SoC設計中,Chip-to-Chip IP在基于AXI的多核分割時也具有重要作用。傳統的TDM方法通常會降低系統運行速度(<= 25MHz),而基于 AXI 的Chip-to-Chip IP則在支持通過 AXI 進行多周期運行的同事

仍保持 50 MHz 以上的系統速度。針對在SoC分割上需要更強大的Chip-to-Chip功能,思爾芯推出自主研發的高速&低延遲AXI Chip-to-Chip IP 方案,Chiplink。Chiplink支持高達 1024 位的 AXI 總線寬度,每組最多可容納4組

AXI 協議。它還支持多種 Serdes 線路速率(12.5G/16.25G/20.625G/25G)以供用戶選擇,使多核Arm之間數據傳輸速率達到100MHz,充分滿足高性能計算的數據傳輸需求。

高帶寬 AXI Transactor – ProtoBridge

思爾芯還配有高帶寬 AXI Transactor — ProtoBridge AXI 協同仿真軟件,該軟件采用業內廣泛使用的 AXI-4 總線協議以及獨有的技術,通過PCIe在PC 主機和 原型驗證平臺之間建立4GB/s的高吞吐量數據通道, 使設計人員提升工作效率,從而縮短驗證周期。

更多信息請聯系我們